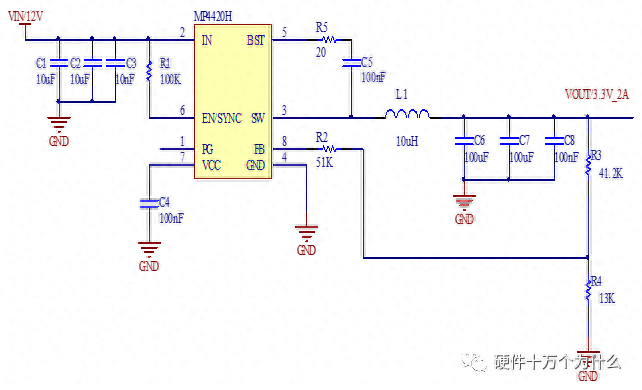

如下图1所示为本模块的电路原理图,具体可以简化为输入部分、控制部分、输出部分以及反馈部分。输入部分:电容C1、C2、C3以及R1;控制部分:MP4420H芯片以及自举电路C5、R5;输出部分:电感L1、电容C6、C7以及C8。反馈部分:电阻R3、R4以及R2。

本模块需要实现一个DC-DC的电源转换功能,其输入为12V,输出为3.3V/2A。选择MP4420H这款芯片,MP4420H的输入范围为4V-36V之间,输出电压范围为0.8V-32.4V,最大输出电流2A。MP4420H的特点有:内置两只开关管且采用同步BUCK的技术、开关频率为450KHZ、内部实现软启动、占空比最大可达到95%以及热关断等。

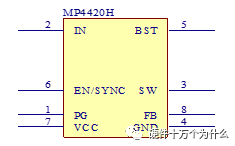

BST:自举引脚端,需要在SW和BST引脚之间连接一个电容以形成浮动电压来驱动MP4420H内上端的开关管。自举电容建议串联一个20欧姆电阻以降低SW尖峰电压。

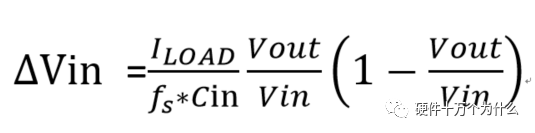

输入电容的主要目的为储能和滤波,以防止输出需要大电流的时候,外部供电模块来不及供电,从而导致输出电压跌落的现象。在选择输入电容的时候首先要保证电容的耐压值为供电模块电压的1.5倍,

为输出电流2A,fs为开关频率450KHZ,Cin为输入电容,Vout为输出电压3.3V,Vin为输入电压12V。本模块选用MP4420H数据手册中推荐的22uF的贴片陶瓷电容,可计算出为44mV。选择两个风华牌10uF/25V的C1和C2贴片陶瓷电容并联,再并联一个电容C3大小为10nF/25V的小电容以滤除输入直流电压中夹杂的高频信号。

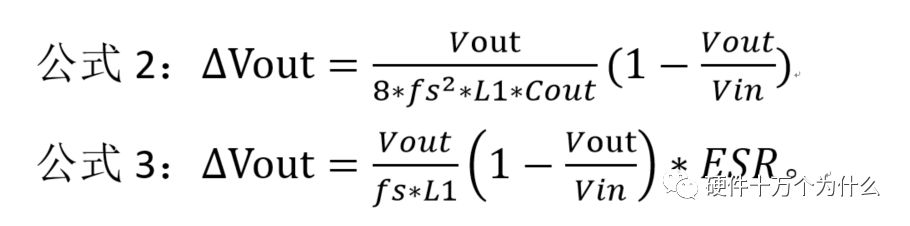

输出滤波电容值可通过计算得到,但是一般在选择电容值的时候通常会选择1.2-2倍计算出的电容值或者更大的电容量,在PCB面积允许的条件下最好多个电容并联。由于输出滤波电容和输出电感会形成两个极点,这会导致电路输出不正常,具体表现为输出纹波较大、输出上升沿有强烈的振荡等。所以在选择电容值的时候也要适当考虑电感值。由MP4420H数据手册可知输出电容和以下公式相关:

L1为输出滤波电感,ESR为输出电容的内阻。故根据输出纹波的要求可大致得到输出电容的大小,在选择电容的时候一般都会选择电容值更大点的电容。对于开关电源模块,电源自身会产生和开关频率一致的电源纹波,始终叠加在电源上输出。输出纹波也会由输出电容的内阻所引起,不断的给输出电容充放电,充电电流在输出电容的内阻ESR两端就会有压降,这个就会产生输出纹波,所以在选择输出电容的时候尽量选择ESR较小的贴片陶瓷电容而不是电解电容,选择几个电容并联也是为了降低输出内阻,一般都会在输出端并联一个较小的电容一般为nF级别的电容以滤去高频纹波。本模块选择两个100uF/16V和一个100nF/16V的贴片陶瓷电容并联。

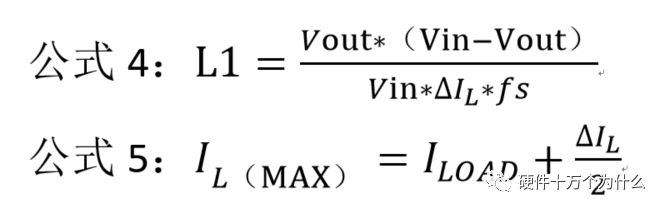

输出电感的主要作用是用来稳定输出电流以及储能,输出电感和输出电容组成的LC滤波电路主要用来平滑输出电压,使输出电压是一个稳定的直流。在选择输出电感的时候,除了要考虑电感值的大小外更要考虑电感所能抑制的电流值。对于BUCK开关变换器的输出电感的电流额定值最少是1.2倍的输出电流。根据MP4420H的数据手册可知,输出电感的电感值在1uH~10uF,电感电流额定值最少为超过负载电流的25%。对于大多数的设计,电感值可由以下公式得到:

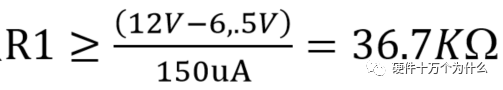

使能电阻R1的选择,EN/SYNC引脚用来控制芯片是否工作,当其为高电平时,芯片就使能工作;当其为低电平时,芯片就不工作。EN/SYNC引脚有一个6.5V的稳压管,连接一个使能电阻到输入端可以使电路使能,流入使能电阻的电流少于150uA,故本模块的使能电阻

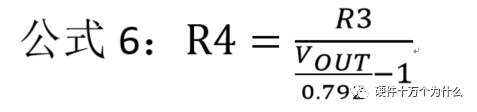

反馈部分电阻的选择,MP4420H通过外接反馈电阻形成一个闭环的电路,从而使输出稳定在3.3V。通过R3和R4的分压得到反馈电压,反馈电压和MP4420H内部的比较器做比较,当反馈电压大于内部比较器的参考电压0.8V时,MP4420H内部的开关管关断,切断输入向输出传递能量。数据手册中推荐R3的大小在40KW左右,本模块选择41.3KW。故可得到R4:

R3和R2用来设置环路带宽,R3和R2越大,带宽越小,环路带宽一般要小于开关频率fs的1/10,以使输出稳定。根据数据手册推荐的R2为51KW。

电源纹波噪声测试是一个比较复杂的测试难题,不同方法测量到的结果不同,即使同一种测试方法不同人测试结果一般也会存在差别。

对于终端类产品,不管是CPU、GPU、DDR等,其芯片内部都有成千上万的晶体管,芯片内不同的电路需要不同的电源供电,常见有Vcore、Vcpu、Vmem、VIO、Vgpu、Vpll等,这些电源有DC-DC电源模块供电,也有LDO电源模块供电,都统一由PMU来管理。

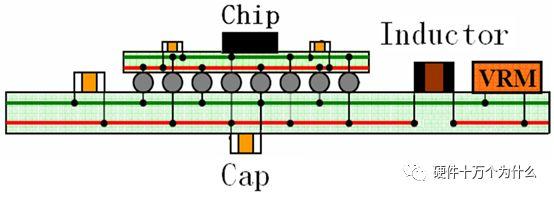

如图3所示,为芯片的PDN图,芯片的供电环路从稳压模块VRM开始,到PCB的电源网络,芯片的ball引脚,芯片封装的电源网络,最后到达die.当芯片工作在不同负载时,VRM无法实时响应负载对电流快速变化的需求,在芯片电源电压上产生跌落,从而产生了电源噪声。对于开关电源模块的VRM,电源自身会产生和开关频率一致的电源纹波,始终叠加在电源上输出。对于电源噪声,需要在封装、PCB上使用去耦电容,设计合理的电源地平面,最终滤去电源噪声。对于电源纹波,需要增大BULK电感或者BULK电容。

对于板级PCB设计,当频率达到一定频率后,由于走线的ESL、电容的ESL的影响,已经无法滤去高频噪声,业界认为PCB只能处理100MHz以内的噪声,更高频率的噪声需要封装或者die来解决。因此对于板级电源噪声测试,使用带宽500M以上的示波器就足够了。一般情况下,示波器的带宽越大,低噪也会随之上升,因此建议测试电源时示波器的带宽限制为1GHz。

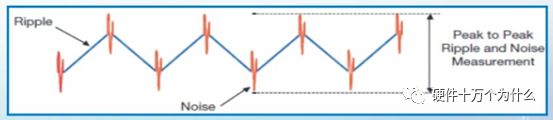

电源纹波和电源噪声是一个比较容易混淆的概念,如下图4所示,蓝色波形为电源纹波,红色波形为电源噪声。电源纹波的频率为开关频率的基波和谐波,而噪声的频率成分高于纹波,是由板上芯片高速I/O的开关切换产生的瞬态电流、供电网络的寄生电感、电源平面和地平面之间的电磁辐射等诸多因素产生的。因此,在PMU侧测量电源输出为纹波,而在SINK端(耗电芯片端,如AP、EMMC、MODEM等)测量的是电源噪声。

电源纹波测量时,限制示波器带宽为20MHz,测量PMU电源输出的波形峰峰值即可电源纹波。由于PMU芯片在设计完成后,芯片厂商会做负载测试,测试PMU在不同负载时输出电源的纹波情况,因此在终端类产品板上,没必要在做这方面的测试,纹波大PMU手册即可。

电源噪声测试时,测试点放在SINK端,由于SINK端工作速度大都在几十MHz以上,因此示波器带宽设置为全频段(最高为示波器带宽上限),测试点要尽量靠近测试芯片的电源引脚,如果存在多个电源引脚,应该选择距离PMU最远端的那个引脚。电源噪声跟PCB布局布线,DECAP电容的位置的位置相关,同时电源噪声影响CPU的工作状态和单板的EMI,终端类产品板需要对每块单板测试电源噪声。

目前芯片的工作频率越来越高,工作电压越来越低,工作电流越来越大,噪声要求也更加苛刻,以MSM8974的CORE核为例,电压为0.9V,电流为3A,要求25MHz时,交流PDN阻抗为22mohm,电源噪声要求在±33mV以内。对于DDR3芯片,要求VREF电源噪声在±1%以内,若1.5V供电,则噪声峰峰值不大于30mV。

示波器有AC和DC两种耦合方式,当采用AC耦合时,其内部等效电路如图5所示,C为隔值电容,R为终端对地阻抗,Vi为输入信号,Vo为测量信号,滤波器的截止频率为

使用无源探头DC耦合测试,示波器内部设置为DC耦合,耦合阻抗为1Mohm,此时无源探头的地线接主板地,信号线接待测电源信号。这种测量方法可以测到除DC以外的电源噪声纹波。

如图6所示,当采用普通的鳄鱼夹探头时,由于地和待测信号之间的环路太大,而探头探测点靠近高速运行的IC芯片,近场辐射较大,会有很多EMI噪声辐射到探头回路中,使测试的数据不准确。为了改善这种情况,推荐用无源探头测试纹波时,使用右图中的探头,将地信号缠绕在信号引脚上,相当于在地和信号之间存在一个环路电感,对高频信号相当于高阻,有效抑制由于辐射产生的高频噪声。更多时候,建议测试者采用第三种测试方法,将一个漆包线绕在探头上,然后将漆包线的焊接到主板地网络上,移动探头去测试每一路电源纹波噪声。同时无源探头要求尽量采用1:1的探头,杜绝使用1:10的探头。

对于示波器,若垂直刻度为xV/div,示波器垂直方向为10div,满量程为10xV,示波器采样AD为8位,则量化误差为10x/256 V。例如一个1V电源,噪声纹波为50mV,如果要显示这个信号,需要设置垂直刻度为200mV/div,此时量化误差为7.8mV,如果把直流1V通过offset去掉,只显示纹波噪声信。

- PAGE