传统CML结构的CTLE基于源极退化实现均衡,当速度提高到56Gb/s或者112Gb/s时CML-based CTLE面临速度、面积、功耗的巨大压力(即使到了7nm工艺节点),本期介绍一种Inverter-Based CTLE以解决传统CTLE的不足。

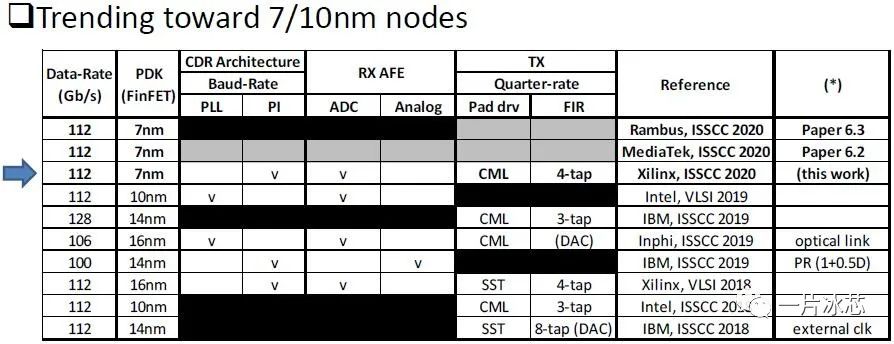

① CDR采用PI-based双环路结构成为主流,双环路结构的优点是PLL环路(PI时钟)和CDR环路可以相互独立,同时多条Lane可共用同一时钟源,节约了功耗和面积;

② RX的DFE均衡变成了ADCDSP结构,将复杂的均衡放到数字域去处理,减小PVT影响,同时便于工艺迁移;

④ 高速SerDes(56Gb/s+)具有超高的技术壁垒,玩家基本都是国外巨头,国内任重道远。

传统RC源极退化CTLE在112Gb/s速率下要保证带宽和线性度变得异常艰难,因为传统CTLE结构较复杂,电源到地通路堆叠的晶体管或电阻较多而且要在低电源电压下保证线性度,为了提高CTLE线性度我们只能进一步减小晶体管或电阻数目,减到最后不就变成Inverter了吗?

图3给出了112Gb/s RX sub-system中Inverter-Based CTLE结构图,合理设置输入输出管的共模电压和摆幅可得到线性增益,在负载管栅端(图中gm,hf和gm,lf)增加RC低通滤波器可实现peaking,采用有源电感(图中gmL)实现带宽拓展,具体工作原理详见第3章。

文献[2]给出了Inverter工作在不同模式下的小信号模型,如图5所示,不同模式下的Inverter可以充当跨导、电阻以及有源电感。

上一篇:场效应管的介绍和用途

下一篇:芯报丨英伟达推出有2080亿晶体管的GB200处理

- PAGE